The Project

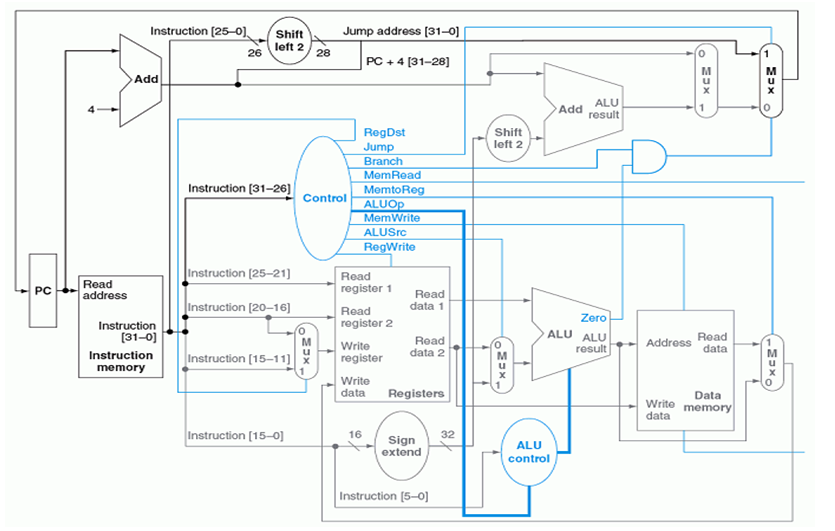

In my Computer Architecture course, I was

tasked with implementing a MIPS processor from

logic gates using VHDL. This project involved

creating a single-stage processor capable of

executing MIPS Assembly instructions. Then, I

recreated it as a pipelined processor.

The project was divided into several stages:

planning the processor, designing individual

components, integrating them into a functional

processor, and pipelining the processor.

Throughout the project, thourough testing was

conducted to ensure proper functionality. By

stating requirements and testing each

component, I was able to effeciently debug the

processor. Once components were integrated, I

tested the processor with a variety of MIPS

assembly code.

This project challenged my understanding of

digital logic, VHDL coding, and the

intricacies of processor design. It was an

invaluable experience that deepened my

knowledge of computer architecture.

The code I created can be found on my GitHub

page,

here.